从上篇文章,咱们能够很明显的看出STA的两大要素,一个是推迟核算,一个是束缚查看。STA最基本的作业之一便是查看途径推迟是否契合束缚。

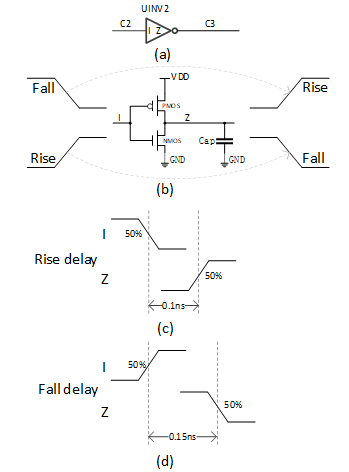

咱们将图一里反相器UINV2的内部MOS电路画出来,来了解cell推迟是怎么产生的:

Rise fall是依照cell的输出翻转(transition)方历来界说的。考虑输入是fall transition,输出是rise transition的景象。一开端,UINV2的输入pin I上的电平是高电平,此刻PMOS处于截止状况,NMOS管处于导通状况,电容的上端通过NMOS管与地接通。只需这个状况继续满意长,电容上的电会被放完,电放完时,UINV2单元的输出pin Z处于低电平状况。接下来,I端开端Fall transition,抵达PMOS的阈值电压后,PMOS管彻底导通,电源通过PMOS管的channel向Cap充电,因为电容的存在,Z端电平呈现一个缓慢上升的进程。

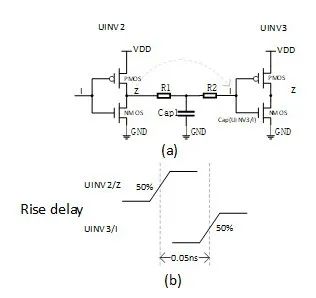

从UINV2的Z输出端到UINV3的I输入端之间是由金属线连接起来的,wire存在寄生的电容电阻。

一般状况,UINV2到UINV3之间的wire寄生参数能够用分布式RC树来建模,作为分布式RC数的简化模型,有T模型和Pi模型。这儿咱们使用了简化的T模型来建模和核算RC推迟。

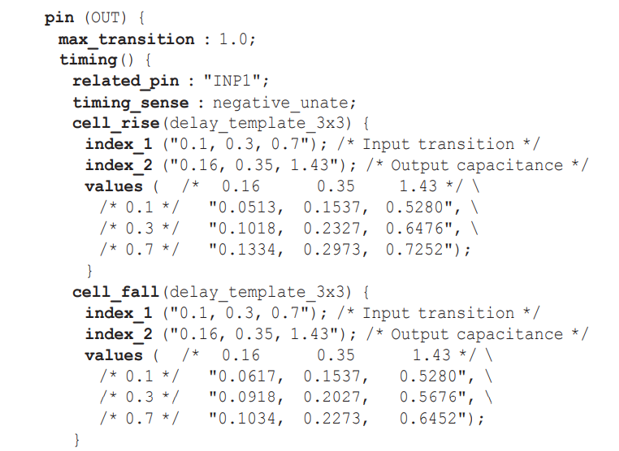

现在,咱们回头再来看一下上面的path delay,它并没有指出其delay是由起点处的rise transition仍是fall transition通过途径传达引起的,所以严格来说,核算式的正确性是值得置疑的。

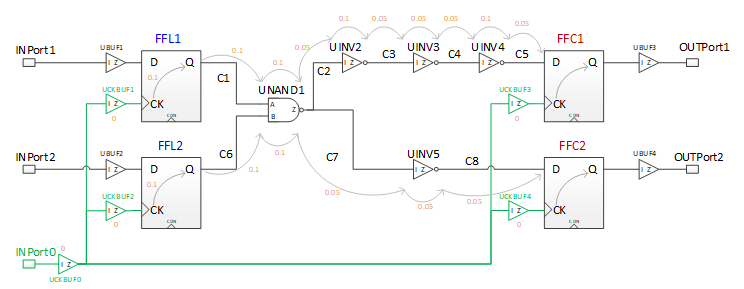

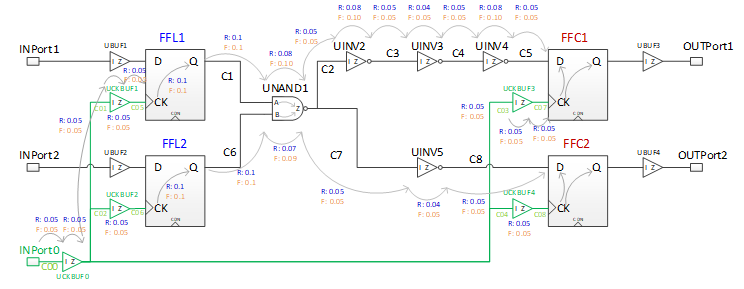

有了上述常识后,咱们从头标示了各个cell和wire的推迟,如图十所示,“R:0.1”代表rise delay是0.1ns,“F:0.1”代表fall delay是0.1ns。一起,咱们从这篇文章开端,将时钟树也归入考虑规模,因而,时钟树上的cell delay和wire delay也标识出来了。

STA东西会核算这4条逻辑途径上的一共8个path delay。然后与时序束缚值做运算,判别是否满意束缚。

想必看到这儿,读者童鞋会对途径推迟有一个大约的了解。下一篇,咱们介绍怎么对这些途径做setup、hold时序查看,以及相关的STA概念。

ballbet安卓子公司

ballbet安卓子公司

投资者关系 股票代码:603738

投资者关系 股票代码:603738